RPMsg-Lite Usage Instructions(Core0 Master)

English | Chinese

Introduction

This project runs on Core1 of RA8P1 (Cortex-M33, 250 MHz) as the remote core in a dual-core system:

Receives commands and data from Core0 (Master) via RPMsg-Lite;

Handles specific tasks (such as communication processing, data acquisition, safety control, and low-power management) and sends results back to Core0;

Supports independent application logic and a message-driven mechanism.

Key Features

Multicore Communication: RPMsg-Lite Remote initialization, endpoint creation, and message transmission/reception.

RT-Thread Support: Independent threads handle message sending and receiving, supporting event/queue synchronization.

Shared Memory & Cache Safety: Uses shared memory reserved by Core0, ensuring cache coherency.

Handshake Mechanism: HELLO/READY/ACK communication with the Core0 Master.

Extensible Protocol Layer: Lightweight protocol examples (Ping/Pong, command frames, data streams).

RPMsg-Lite Instructions

RPMsg-Lite is a lightweight implementation of Remote Processor Messaging (RPMsg), primarily used in multi-core processor systems to enable data exchange and message passing between different cores. It is based on the OpenAMP framework and leverages shared memory and virtual channels (Virtio Channels) to achieve efficient and reliable inter-core communication in resource-constrained embedded systems.

1. Design Background

In multi-core MCUs or SoC systems, different cores may execute different types of tasks, for example:

Cortex-M cores run real-time control tasks

Cortex-A cores run operating systems or high-level applications

In such cases, an efficient communication mechanism is needed to exchange data or trigger events between cores. RPMsg-Lite provides a lightweight, easy-to-use, and reliable message-passing solution.

2. Key Features

Lightweight

Compared with full RPMsg implementations, RPMsg-Lite consumes less memory and CPU resources, making it ideal for resource-constrained embedded systems.

Core data structures and queue mechanisms are optimized to minimize memory copies.

Inter-core Communication

Supports communication between different cores.

Uses shared memory as a data buffer, with messages transmitted via virtual channels.

Reliability

Provides reliable message delivery mechanisms to ensure messages are neither lost nor duplicated.

Configurable message queue lengths allow for high-reliability data transmission.

Flexibility

Supports static or dynamic creation of communication channels to adapt to different system architectures.

Simple Interface

Offers easy-to-use APIs for sending, receiving, and managing channels.

Developers can integrate it quickly without needing to understand the underlying shared memory or interrupt mechanisms.

3. Working Principle

RPMsg-Lite is based on the virtio virtual device mechanism:

Shared memory stores message data and queue information.

The sending core writes messages to the shared memory queue and notifies the receiving core via an interrupt.

The receiving core reads the messages and processes them according to application requirements.

After processing, the receiving core can send acknowledgment messages to ensure communication reliability.

4. Application Scenarios

Dual-core or Multi-core MCU systems: For example, in the RA8P1 dual-core MCU, M85 handles high-performance tasks while M33 handles real-time tasks, with communication between the cores via RPMsg-Lite.

Real-time task separation: Time-sensitive tasks and high-level application tasks can run separately to improve system performance.

Resource-constrained embedded systems: Low memory footprint and communication overhead make it suitable for industrial control, robotics, automotive electronics, and other fields.

Hardware Description

None

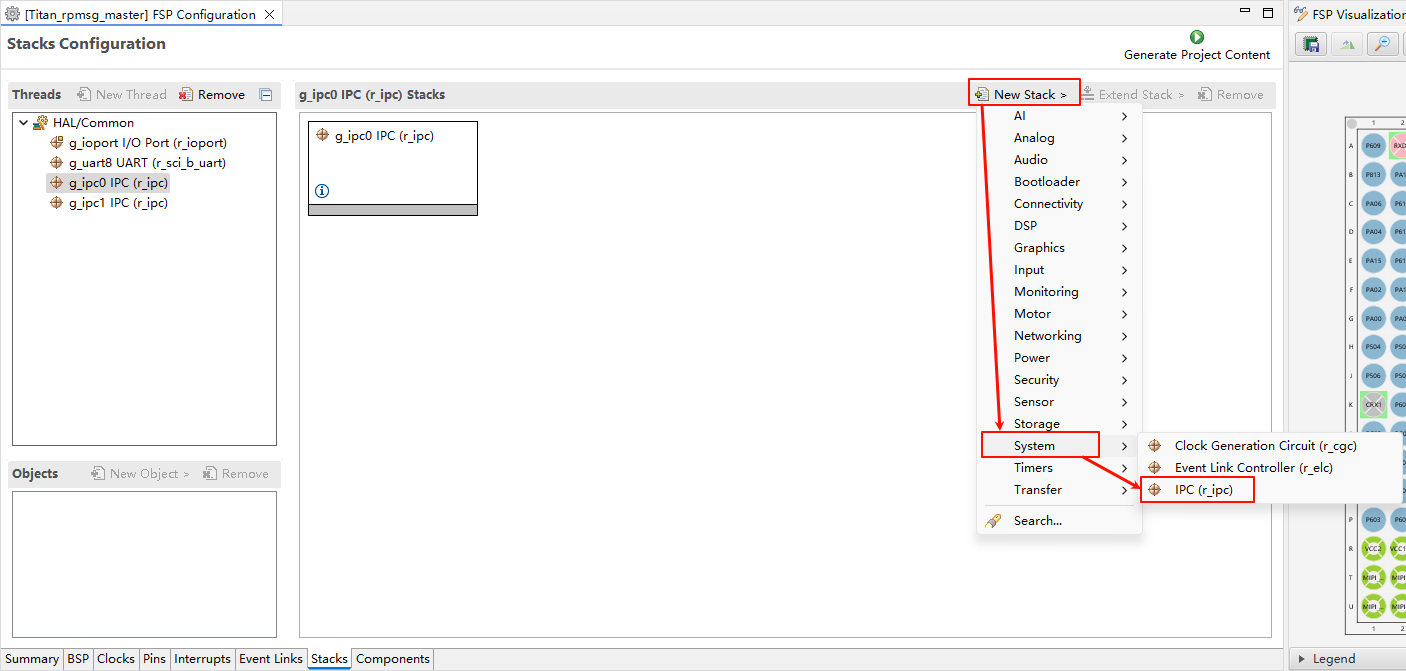

FSP Configuration

Create two

r_ipcstacks:

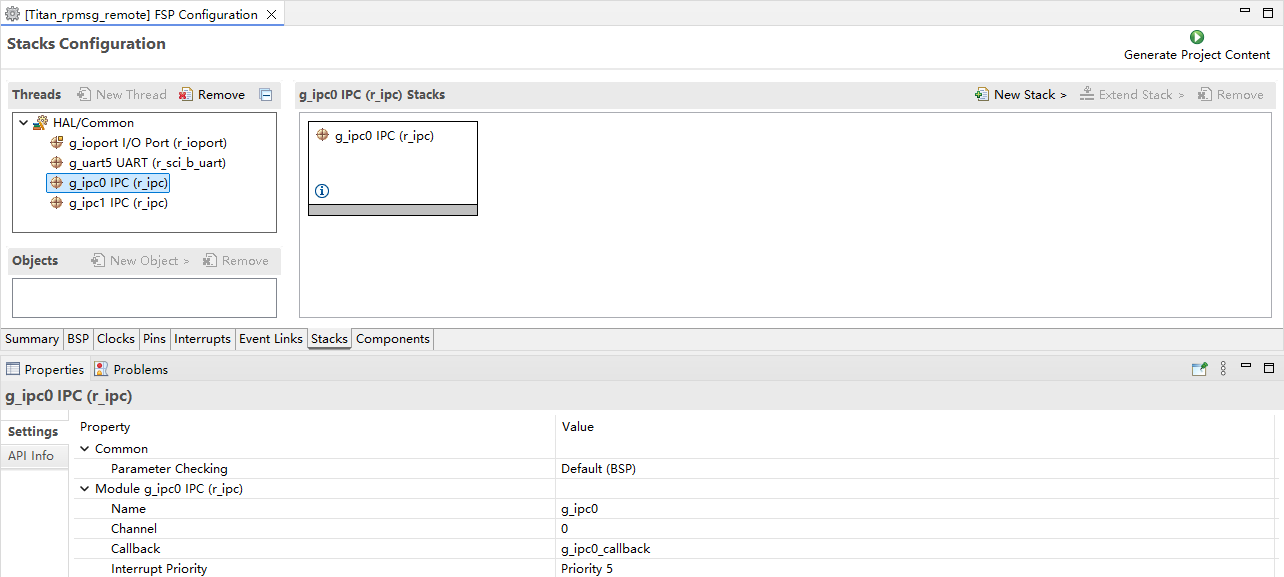

Configure IPC0:

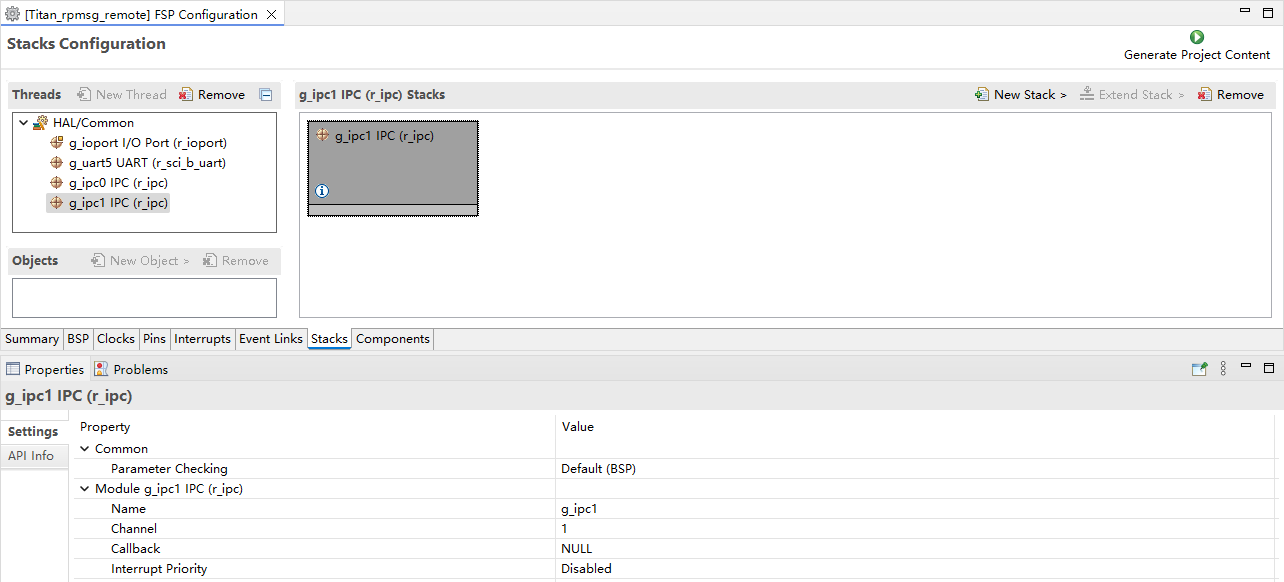

Configure IPC1:

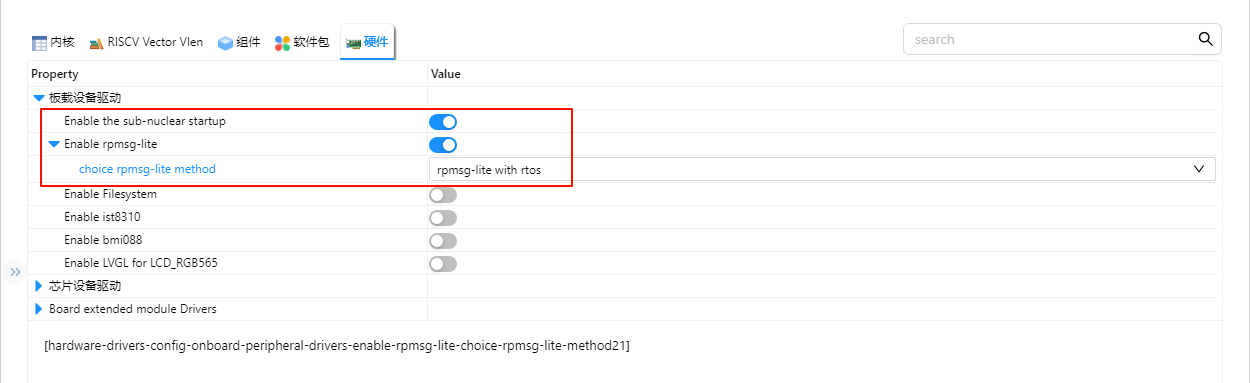

RT-Thread Settings Configuration

Enable sub-nuclear startup and rpmsg-lite。

Example Code Description

The sample program is located at /board/ports/rpmsg-adapt.

Compilation & Download

RT-Thread Studio: In RT-Thread Studio’s package manager, download the Titan Board resource package, create a new project, and compile it.

Download Methods

Currently, DAP-Link does not support programming the Core1 firmware, so you need to use the Renesas Flash Programmer tool to program the firmware. The detailed programming steps are as follows:

Download and install the Renesas Flash Programmer tool: Renesas Flash Programmer (Programming GUI) | Renesas.

Connect the USB-DEV port of the development board to the PC.

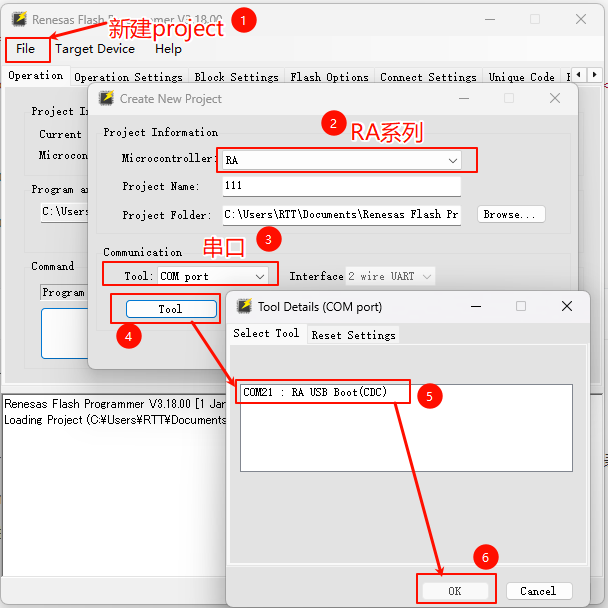

Create a project: The development board needs to enter BOOT mode (hold down the BOOT button and press the RESET button once).

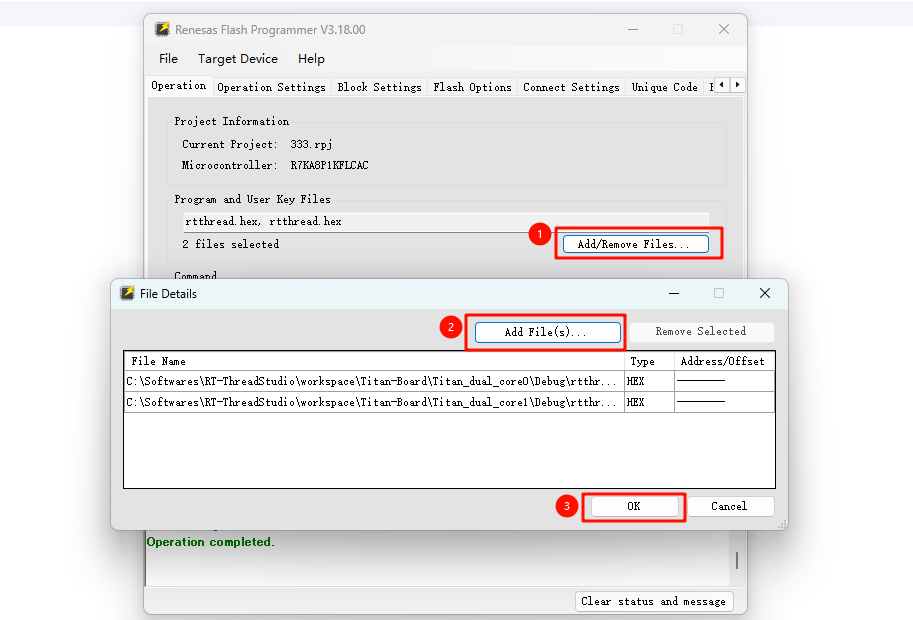

Select the firmware to be programmed:

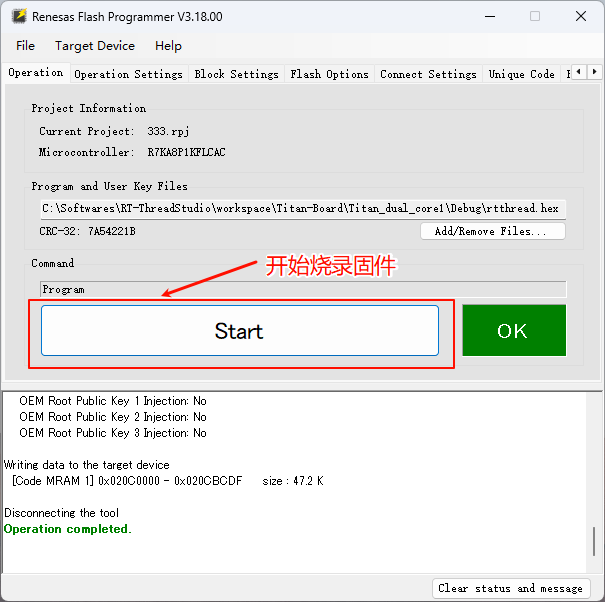

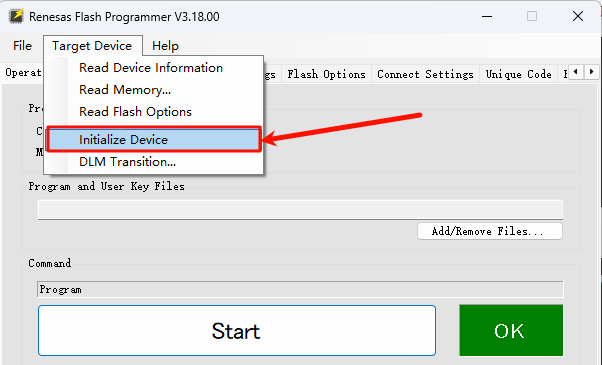

Flashing firmware (at this time, the development board must be in BOOT mode):

Run Effect

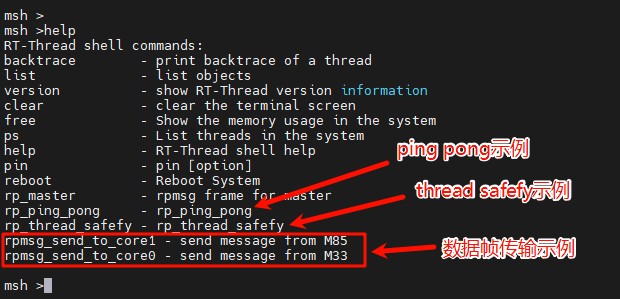

Note: In the RPMsg-Lite example project, before running the ping pong, thread safety, and data frame transmission examples shown below, you must first start the remote endpoint on Core1.

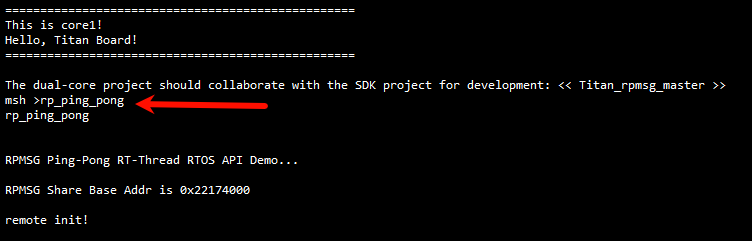

Ping Pong Example

On Core1, enter the command rp_ping_pong to initialize the remote endpoint. Then, on Core0, enter the same rp_ping_pong command to start the master.

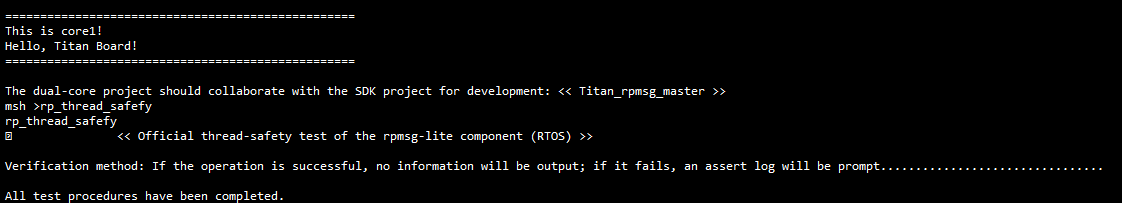

Thread Safety Example

On Core1, enter the command rp_thread_safefy to initialize the remote endpoint. Then, on Core0, enter the same rp_thread_safefy command to start the master.

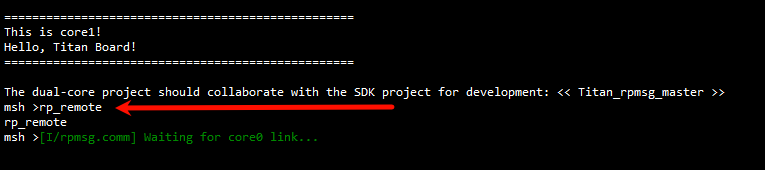

Data Frame Transmission Example

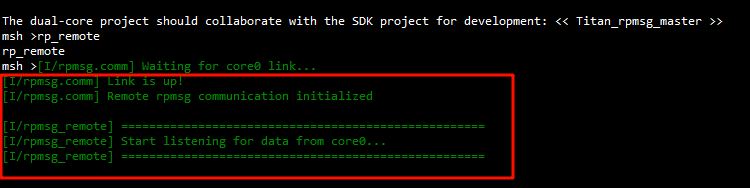

On Core1, enter the command rp_remote to start the remote endpoint. Then, on Core0, enter the command rp_master to start the RPMsg master.

After the master starts on Core0, the terminal will display the following message, indicating that the connection has been successfully established.

You can then use the rpmsg_send_to_core0 command to transmit data to Core0.

Notes on Using Dual-Core Projects

DAP-Link does not currently support dual-core projects. Please use Renesas Flash Programmer (RFP) for downloading, or replace the DAP-Link firmware with another debugging firmware (a tutorial is available on the RT-Thread community forum).

Before downloading a dual-core project, it is recommended to use Renesas Flash Programmer to erase the Flash memory.

When configuring FSP for dual-core projects, Core0 and Core1 must not configure the same peripheral or pin simultaneously. For example: if UART8 is configured in Core0’s FSP, then UART8 must not be configured again in Core1’s FSP.